# Simulating the Coupling between metal lines in milimeter wave frequencies

Fontounasios Christos<sup>1</sup>, Alkis Hatzopoulos<sup>2</sup>

Department of Electrical and Computer Engineering,

Aristotle University of Thessaloniki, Greece.

<sup>1</sup>chfontou@auth.gr, <sup>2</sup>alkis@eng.auth.gr

Abstract— A study of the impact of metal ground shields on the coupling between two metal lines is presented. The structure is designed over a bulk silicon substrate with epitaxial layer, so the coupling through the substrate is also involved. A lightly doped profile is adopted and is simulated by means of an electromagnetic simulator for various line distances and different metal layers, assuming a 65 nm bulk CMOS technology. The impact of various metal layer ground shields placed below the line layer is examined . Furthermore, the increase of isolation (resulting in reduction of the noise coupling) between the lines by dividing the ground shield into smaller area ground shields, is also analyzed. Finally the impact of the distance's width between the divided ground shields is examined. S parameters are used to compare the various structures.

Index Terms— Substrate noise; Metal line coupling; Ground shield.

# I. INTRODUCTION

As the CMOS technology increases its scaling, substrate noise coupling considerations become more important. Applications implemented in high frequencies up to 100 GHz like e.g. automotive radar or backhaul radio links require thorough study of this area in order to become more reliable [1]. In this study a lightly doped substrate is examined which corresponds to the one commonly used in modern 65nm CMOS technologies.

Simulations are conducted using a Method of Moments (MOM) 3D planar electromagnetic simulator. Simulating the exact structures including the ICs' various isolation layers can be extremely demanding in terms of computer resources and time. Thus approximating structures are analyzed below, in order to reduce the complexity of the structure and achieve faster results.

Many techniques have been suggested in order to reduce the coupling between the various interconnections and between the elements of an integrated circuit, e.g. integrated inductors. Metal guard rings for example and metal ground shields have been examined in the cases of lower frequencies [2-3]. In this study, metal ground shields are implemented to examine the reduction of the coupling noise between an aggressor and a victim metal line up to 100GHz. Different cases of ground shields are studied including different metal ground shields, divided ground shields into two or six smaller area ground shields in order to reduce the capacitive coupling between the metals that interfere and thus to improve the isolation on the substrate.

#### **II. SUBSTRATE STRUCTURE**

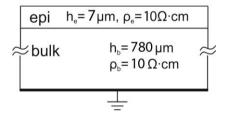

The carrier concentration and mobility determines conductivity in the substrate. Thus, the doping profile is the parameter that defines the conductivity of the substrate. Furthermore, conductivity defines the noise transmission through the substrate. A major modern process technology used in the memory and RF processes, has a high resistivity substrate. This substrate is manufactured through a lightly doping process of the bulk and the epi layers of the substrate. High resistivity substrates are used for RF applications since noise isolation is critical to minimize eddy currents in the substrate and enhance the quality factor of all passive devices built on them. Fig. 1 shows the typical layer stack up for the process, along with the typical values in this case. A relatively high resistivity value of 10  $\Omega$  cm is used in the bulk. On top of it lies an epitaxial layer of the same resistivity [4-6].

Figure 1. Doping profile of the layer stack-up of the simulated lightly doped process.

Coupling through substrate and modeling has not been studied thoroughly up to the frequencies of 100 GHz. The noise signal that passes from the aggressor through the substrate to the victim line and to the grounded plane is the most important factor that should be examined [7].

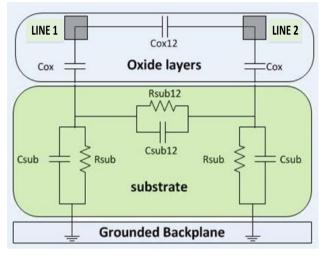

The simulated structure of this study is constituted of two metal lines, with an area of  $10x30\mu m^2$ . These metal lines are placed at a certain metal layer and the structure is simulated for a certain distance between them. Additionally a metal ground shield is inserted at a layer below the metal lines. The substrate is either modeled by a two port  $\pi$ -resistance network or by an RLCG parallel line model or by other analytical models such as quasi-static (QS) and magnetic potential (MP) models [8-10],. Here the extracted s-parameters are used to analyze and

compare the various simulated structures. The  $S_{12}$  parameter defines the signal that passes from the aggressor metal line to the victim. Fig. 2 describes a proposed model that is used to draw conclusions and compare the results. Its lumped elements are described in Table I. To approximate the electrical resistance and the capacitance of bulk and epi layers, the expressions (1) and (2) can be used respectively. Whereas S is the area of overlap of the two plates, *l* is the separation between the plates.

$$R = \rho \frac{l}{S} \tag{1}$$

$$C = \varepsilon_r \varepsilon_0 \frac{S}{l} \tag{2}$$

(a)

Figure 2. Electrical model of the substrate.

| TABLET                    |                                                  |  |

|---------------------------|--------------------------------------------------|--|

| ELEMENTS OF THE STRUCTURE |                                                  |  |

| Element                   | Description                                      |  |

| $C_{ox1} = C_{ox2}$       | Capacitance between the line and the epi layer   |  |

| C <sub>ox12</sub>         | Capacitance between the two lines                |  |

| $C_{sub1} = C_{sub2}$     | Capacitance due to the substrate                 |  |

| $R_{epi1} = R_{epi2}$     | Resistance of the epi layer                      |  |

| $R_{epi12}$               | Resistance between the two lines through the epi |  |

|                           | layer                                            |  |

| $R_{bulk1} = R_{bulk2}$   | Resistance of the bulk layer                     |  |

| R <sub>bulk12</sub>       | Resistance to the ground                         |  |

|                           |                                                  |  |

TADLEI

# **III. SIMULATION RESULTS**

A. Using metal ground shields to reduce the noise coupling.

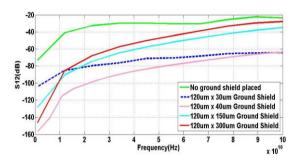

At first we calculated the isolation in a case without a ground shield when metal line distance was equal to 100um.

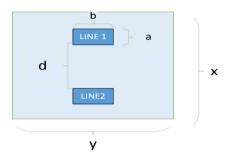

Afterward a grounded metal shield of x=120um width and a y length that varies from 30um to 300um is placed at a layer below the lines layer as shown in fig. 3. The ground shield is constructed in metal 1 metal 3 or metal 5.. The resulting S<sub>12</sub>parameters between the two metal lines are shown in fig. 4, for metal lines at the 7<sup>th</sup> metal layer and the ground shield being placed at 5<sup>th</sup> metal layer. The results lead to the intuitive conclusion that using a grounded metal shield at a layer below the metal lines layer, reduces considerably the coupling noise between the two metal lines. By placing the metal shield below the metal lines, we keep the electromagnetic fields from entering the silicon substrate thus we reduce the substrate loss.

Figure 3. The two metal lines of a=10 width and b=30 um lengh. Metal line distance is 100 um. At a metal layer below we have placed a ground shield of x=120 um width and y=30 um, 40 um, 150 um and 300 um length.

|         | TABLE II<br>Elements Of The Structure |                            |

|---------|---------------------------------------|----------------------------|

| Element | Description                           | Values                     |

| a       | Width of the metal line               | 10um                       |

| b       | Length of the metal line              | 30um                       |

| d       | Distance between the metal lines      | 100um                      |

| х       | Groumd shield width                   | 120um                      |

| у       | Ground shield length                  | 30um,40um,<br>150um, 300um |

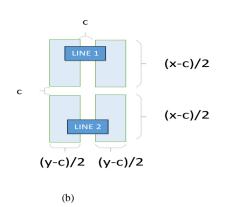

## B. Isolation provided by different size ground shields

In figure 4 we simulated the cases where the ground shields area varies from  $120x30um^2$  to  $120x300um^2$ . As it can be observed the bigger the area of the ground shield is, the worse

the isolation becomes. This happens due to the fact that bigger area ground shields features more metal, thus capacitive coupling is bigger, leading to worse isolation. We can notice that the best isolation provided by the structure occurs for a ground shield of an area around 120x40um<sup>2</sup>. Smaller ground shield areas lead to the deterioration of the providing isolation as it is shown in figure 4. This happens because the ground shields metal size is not enough to keep all the electromagnetic fields from entering the silicon substrate.

Figure 4 Comparison of S12 parameters in cases with and without a ground shield placed in metal 5 with lines placed in metal 7 and a metal line distance of 100um. The ground shields area vary from 120x30um<sup>2</sup> to 120x300um<sup>2</sup>

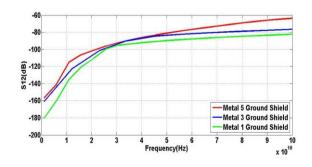

### C. Isolation for ground shields at different metal layers

In figure 5 we simulated the cases where the ground shield is placed at metal 1, metal 3 and metal 5 layers. The lines were placed at metal 7 layer and the distance between the lines was 100um. As it can be observed, the lower the layer where the metal shield is placed, the better the isolation becomes. This happens because the bigger the distance is between the metal layers, the less the capacitive coupling that will occur between them. Big capacitive coupling leads to worse isolation so we need to minimize the capacitive coupling phenomenon.

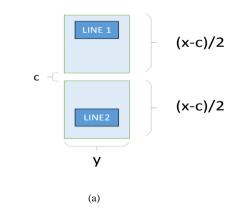

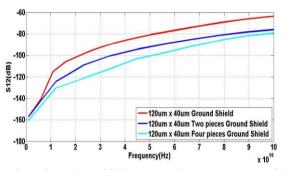

#### D. Dividing ground shield to improve isolation

The structures where the ground shields are divided into smaller area ground shields, were studied. In the previous chapter we studied different size ground shields, coming in conclusion that the best isolation provided by the substrate occurs when the area of the ground shield is 120x40um<sup>2</sup>. Thus in next simulations we will use this specific area of 120x40um<sup>2</sup>. Two cases were simulated. In the first case the ground shield is divided into two ground shields with a space of 6um . The total area included by the two ground shields and the space between them is equal to  $120x40um^2$ . Thus the width of each ground shield is equal to A=(x-c)/2=57umwidth. The length of each of the ground shields is equal to y=40um. In the second case the  $120x40um^2$  ground shield is divided into four ground shields with spaces of 2um. The total area included by the four ground shields and the spaces between them is again equal to  $120x40 \text{ um}^2$ . Thus the width of each ground shield is equal to A=(x-c)/2=57um and the length of each ground shield is equal to B=(y-c)/2=17um. The two cases are presented in Figure 6a and Figure 6b.

In figure 7 we simulated the first case where we have divided the ground shield into two smaller area ground shields and the second case where we divided it into four ground shields. The ground shields were placed in metal 5 layer and the metal lines in metal 7 layer. The structures were simulated for 100um line distance. As it can be observed, the more the times we divide the ground shield of  $120x40um^2$  into smaller area ground shields keeping the total width and length of the geometry at the same levels ( $120x40um^2$ ), the better the isolation becomes. This happens because when we divide the ground shield to a larger number of ground shields, we use less metal since the area that remains uncovered by metal is bigger. Thus less metal usage leads to smaller capacitive coupling that leads to better isolation.

Figure 5.  $S_{12}$  parameters for various grounded metal shields. Distance from line to line is 100 $\mu$ m, and lines are placed at metal 7 layer.

Figure 6. The geometry of the two structures where the ground shield is divided into (a)two and (b)four pieces. The total lentgth and width of the geometry remains same and equal to  $120x40um^2$ . The width of the ground shields in both cases is equal to A=(x-c)/2=57um and the length in 1<sup>st</sup> case is equal to y=40. In second case the length is equal to B=(y-c)/2=17um. Distance between metal lines is 100um.

Figure 7. Comparison of S12 parameters in cases where the unified ground shield is divided into two and into four smaller area ground shields. Ground shields are used in metal 5 layer whilst metal lines are used in metal 7 layer.

### IV. CONCLUSIONS AND FURTHER WORK

The substrate noise coupling issue between two metal lines was studied in this work. A lightly doped profile was examined and its impact to the coupling level of various structures was investigated. Moreover, different metal layers were utilized for the simulations and the effect of a metal ground shields under the metal lines was investigated.

In the lightly doped processes,

- The use of ground shields in various metal layers below the metal lines layer, leads to better isolation because ground shields prevent electromagnetic field from entering the substrate.

- Ground shields of smaller size offer a better isolation due to the lower capacitive coupling between the metals. However after decreasing the size of the ground shield to a minimum level, the

isolation worsens. That happens because the metal amount is too low to be able to prevent the electromagnetic field from entering the substrate.

- Ground shields placed in lower metal levels lead to better isolation due to lower capacitive coupling between the metals that interfere.

- Dividing the ground shield but keeping the width and the length of the geometry intact, leads to better noise isolation due to the fact that less metal is used thus capacitive coupling between metals used is lower.

Further study is needed to examine more complicated geometries and designs of ground shields and check their impact on substrate noise coupling. Moreover other designing solutions are examined in order to reduce the metal coupling through substrate and improve the isolation of the ICs in frequencies up to 100 GHz. The parameters of a lumped circuit model, like the one in fig. 2, are also to be calculated using analytical and/or fitting techniques.

#### REFERENCES

- Jyh-Chyurn Guo and Yi-Min Lin, "A New Lossy Substrate Deembedding Method for Sub-100 nm RF CMOS Noise Extraxtion and Modelion" in IEEE Transactions on electron devices, Vol. 53, No2, February 2006, pp. 339-347.

- [2] Mat, D.A.A., Pokharel, R.K., Sapawi, R., Kanaya, H., Yoshida, K., " 60GHz-band on-chip Marchand Balun designed on flat and patterned ground shields for milimeter-wave 0.18μm CMOS technology", IEEE Microwave Conference Proceedings (APMC), 2011 Asia-Pacific, pp. 884-887.

- [3] Rautio, J.C., Merrill, J.D., Kobasa, M.J.," Efficient electromagnetic analysis of spiral inductor patterned ground shields", 2013 IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems (COMCAS),2013,pp 1-5.

- [4] Ahmed Helmy, Mohammed Ismail, "Substrate noise coupling in RFICs", Analog Circuits and Signal Processing series, Springer,2008

- [5] Hai Lan, Zhiping Yu and Robert W. Dutton, "A CAD-Oriented Modeling Approach of Frequency-Dependent Behavior of Substrate Noise Coupling for Mixed-Signal IC Design" in Proc. of the Fourth International Symposium on Quality Electronic Design (ISQED'03), 2003, pp. 195-200.

- [6] Gholan Reza Karimi and Ebrahim Akbari, "An efficient technique for accurate modeling and simulation of substrate coupling in deep micron mixed-signal ICs", International Conference on Electronic Devices, Systems and Applications (ICEDSA2010), 2010, pp. 88-92.

- [7] Harpreet Parashar and Ghanshyam Singh, "Effects of capacitive and inductive coupling on interconnects at RF Frequencies", Devices and Communications (ICDeCom), 2011 International Conference, pp. 1-5.

- [8] Madhumanti Datta, Susmita Sahoo, Rajib Kar, "Bandwidth Modelling for Distributed On-Chip RLCG Interconnect Considering Coupling Effects", International Conference on Devices and Communications (ICDECom), 2011,pp. 1-5.

- [9] Georgios Veronis, Yi-Chang Lu, and Robert W. Dutton, "Modeling of Wave Behavior of Substrate Noise Coupling for Mixed-Signal IC Design", Proceedings of the 5th International Symposium on Quality Electronic Design, 2004, pp 303-308.

- [10] Aboul-Yazeed, M.S.; El-Rouby, A.; Hussien, A., "Lumped elements model for substrate noise coupling," Electronics, Communications and Photonics Conference (SIECPC), 2013 Saudi International, pp.1-5, 27-30 April 2013.